- 您现在的位置:买卖IC网 > Sheet目录3870 > PIC16F1946-I/PT (Microchip Technology)IC MCU 8BIT FLASH 64TQFP

PIC16(L)F1946/47

DS41414D-page 144

2010-2012 Microchip Technology Inc.

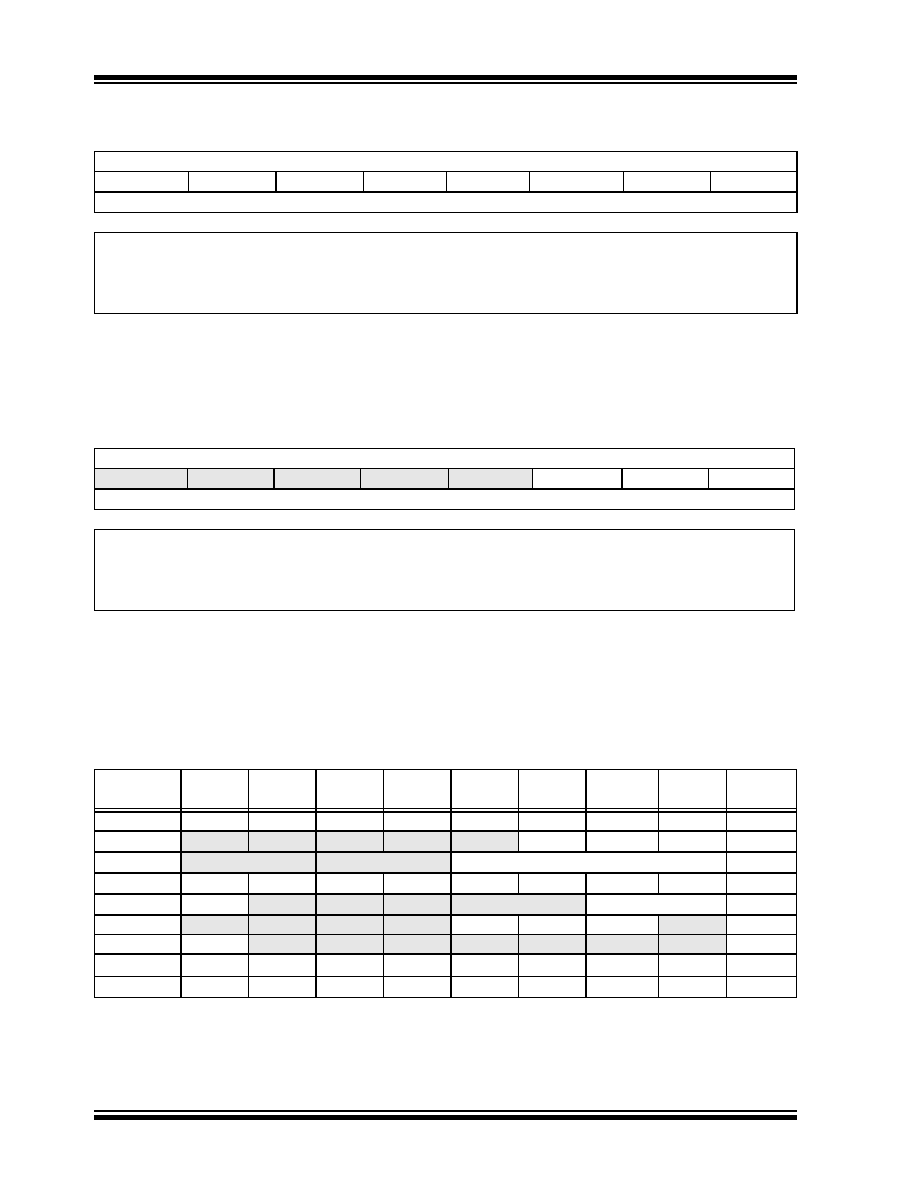

TABLE 12-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

REGISTER 12-18: LATE: PORTE DATA LATCH REGISTER

R/W-x/u

LATE7

LATE6

LATE5

LATE4

LATE3

LATE2

LATE1

LATE0

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

u = Bit is unchanged

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

‘1’ = Bit is set

‘0’ = Bit is cleared

bit 7-0

LATE<7:0>

: PORTE Output Latch Value bits(1)

Note 1:

Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of

actual I/O pin values.

REGISTER 12-19: ANSELE: PORTE ANALOG SELECT REGISTER

R/W-1

—

ANSE2

ANSE1

ANSE0

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

u = bit is unchanged

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

‘1’ = Bit is set

‘0’ = Bit is cleared

bit 7-0

ANSE<7:0>

: Analog Select between Analog or Digital Function on Pins RE<7:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input(1). Digital input buffer disabled.

Note 1:

When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow

external control of the voltage on the pin.

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Register

on Page

APFCON

P3CSEL

P3BSEL

P2DSEL

P2CSEL

P2BSEL

CCP2SEL

P1CSEL

P1BSEL

ANSELE

—

ANSE2

ANSE1

ANSE0

CCPxCON

PxM<1:0>(1)

DCxB<1:0>

CCPxM<3:0>

LATE

LATE7

LATE6

LATE5

LATE4

LATE3

LATE2

LATE1

LATE0

LCDCON

LCDEN

SLPEN

WERR

—

CS<1:0>

LMUX<1:0>

LCDREF

LCDIRE

LCDIRS

LCDIRI

—

VLCD3PE VLCD2PE

VLCD1PE

—

LCDSE2

SE31

SE30

SE29

SE28

SE27

SE26

SE25

SE24

PORTE

RE7

RE6

RE5

RE4

RE3

RE2

RE1

RE0

TRISE

TRISE7

TRISE6

TRISE5

TRISE4

TRISE3

TRISE2

TRISE1

TRISE0

Legend:

x = unknown, u = unchanged, – = unimplemented locations read as ‘0’. Shaded cells are not used by PORTE.

Note 1:

Applies to ECCP modules only.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16LF1939-I/ML

IC MCU 8BIT FLASH 44QFN

PIC18LF6493-I/PT

IC PIC MCU FLASH 8KX16 64TQFP

DSPIC33FJ64GP310T-I/PT

IC DSPIC MCU/DSP 64K 100TQFP

DSPIC33FJ64GP310T-I/PF

IC DSPIC MCU/DSP 64K 100TQFP

PIC16C622A-20I/SO

IC MCU OTP 2KX14 COMP 18SOIC

PIC18LF14K50-I/SO

IC PIC MCU FLASH 16KB 20-SOIC

XF2M34151L

CONN FPC 34POS 0.5MM PITCH SMD

XF2M30151L

CONN FPC 30POS 0.5MM PITCH SMD

相关代理商/技术参数

PIC16F1946T-I/MR

功能描述:8位微控制器 -MCU 14KB 512B RAM 256B EEPROM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1946T-I/PT

功能描述:8位微控制器 -MCU 14KB Flash, 512B RAM LCD, 1.8-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1947-E/MR

功能描述:8位微控制器 -MCU 28KB1KB RAM 256B EEPROM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1947-E/PT

功能描述:8位微控制器 -MCU 28KB Flash, 1KB RAM LCD, 1.8-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1947-I/MR

功能描述:8位微控制器 -MCU 28KB1KB RAM 256B EEPROM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1947-I/PT

功能描述:8位微控制器 -MCU 28KB Flash, 1KB RAM LCD, 1.8-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1947T-I/MR

功能描述:8位微控制器 -MCU 28KB1KB RAM 256B EEPROM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1947T-I/PT

功能描述:8位微控制器 -MCU 28KB Flash, 1KB RAM LCD, 1.8-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT